Next-Generation Audio DSP Performance in Software-Defined Vehicles

Consumer and automotive audio technology is advancing rapidly, with market trends like generative AI-based audio processing, immersive soundscapes, and advanced infotainment in software-defined vehicles driving the need for enhanced audio DSP performance. However, the demand for increased compute power cannot be met by a single DSP, and using multiple DSPs presents significant programming challenges.

Today, OEMs and SoC vendors are required to handle all multicore hardware design and software development independently, while facing pressure to bring products to market quickly. This has led to complexities in software-based synchronization and task partitioning across multicore clusters, often resulting in performance shortcomings. In this evolving landscape, a pre-designed hardware solution with multicore-enabling operating software is essential to streamline hardware design and simplify the software complexity of developing multicore audio products.

Multicore Innovations for Enhanced Performance

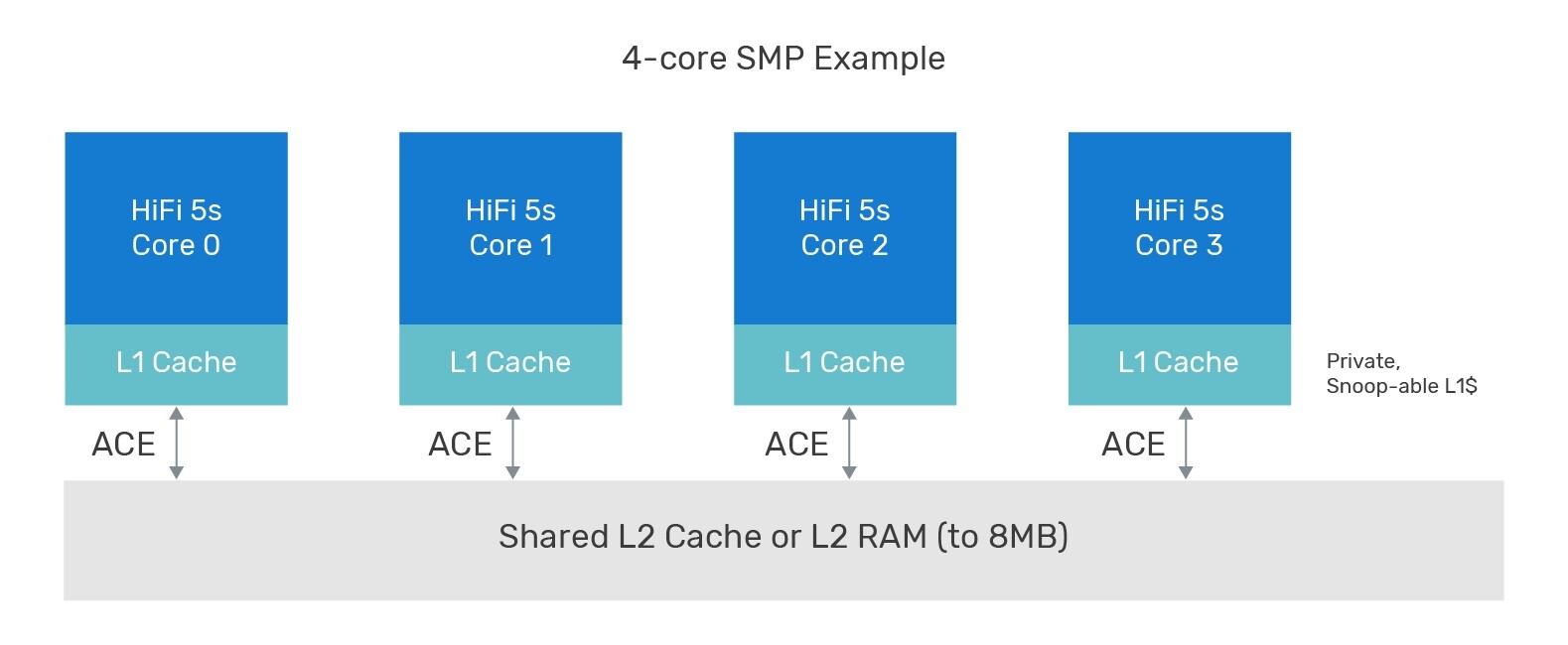

To address the challenges of programming multiple DSPs, Cadence has enhanced its Xtensa LX8 Platform with symmetric multiprocessing capabilities. The new Xtensa Multicore LX8 Platform enables SoC designers to create clusters of up to eight symmetric multiprocessors (SMP) with hardware cache coherency.

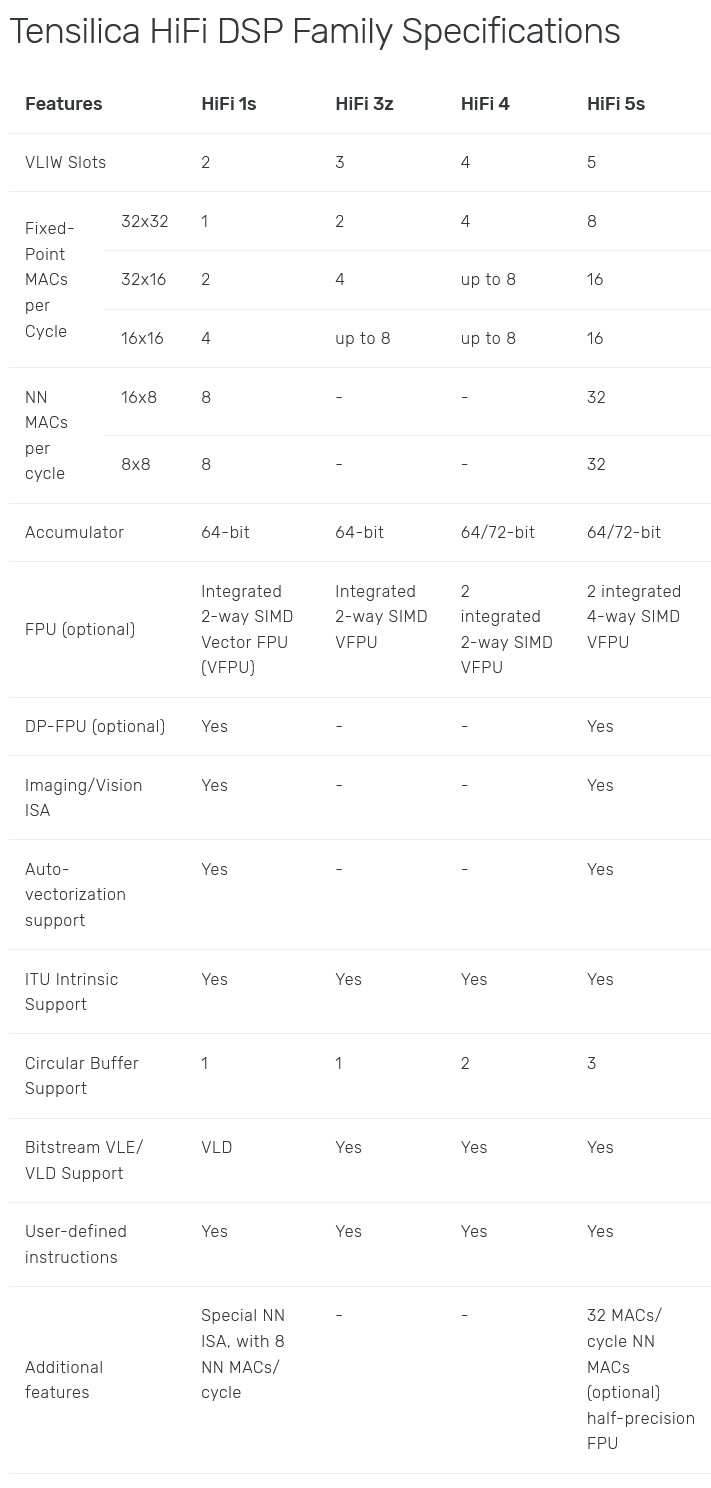

Building on the success of the Tensilica HiFi 5s DSP, Cadence has introduced the Tensilica Cache-Coherent HiFi 5s SMP, the first product based on the new platform. This product offers scalable performance, higher resource utilization, and simplified software development for a wide range of audio DSP applications.

Benefits of Cache-Coherent HiFi 5s SMP

The Tensilica Cache-Coherent HiFi 5s SMP is designed for high-performance, low-power audio applications and can scale from two to eight cores. It integrates features like interrupt distribution and cross-core debug capabilities. Application development is supported by Zephyr and FreeRTOS, with future support planned for XOS, Cadence's RTOS.

Customers can easily download the multicore cluster from Cadence's Xtensa Processor Generator (XPG) and receive a complete Software Development Toolkit (SDK) for multicore development. The multicore-aware RTOS manages task distribution and cross-core synchronization, while cache coherency ensures efficient memory utilization and performance scaling.

Partner Support and Customer Benefits

Partners like Dolby Laboratories and DSP Concepts have praised the Cache-Coherent HiFi 5s SMP for its innovative audio capabilities and ease of integration. The hardware cache coherency eliminates software synchronization issues, resulting in higher product quality and faster time-to-market. The SMP architecture allows audio applications to achieve optimal performance based on the number of cores, with easy adaptation to changing requirements.

Cadence's focus on ease of programming and software reliability aims to provide customers with a competitive edge in the evolving audio technology landscape. The configurable Tensilica Cache-Coherent HiFi 5s SMP offers scalability, resource utilization, and accelerated time-to-market for audio products.

With early customer adoption already underway, the Cache-Coherent HiFi 5s SMP is now available, offering multicore examples in the SDK for quick implementation.